Researchers at the Massachusetts Institute of Technology (MIT) have developed a new superconducting memory array that significantly reduces error rates compared to previous models. Published on January 25, 2026, in the journal Nature Electronics, this innovation could propel the development of energy-efficient quantum computers.

Superconducting memories, which utilize materials that conduct electricity without resistance at low temperatures, hold promise for enhancing the performance of quantum computing systems. These advanced memory components are essential for executing complex tasks efficiently. However, existing superconducting memory devices often suffer from high error rates and scalability challenges, limiting their practical applications.

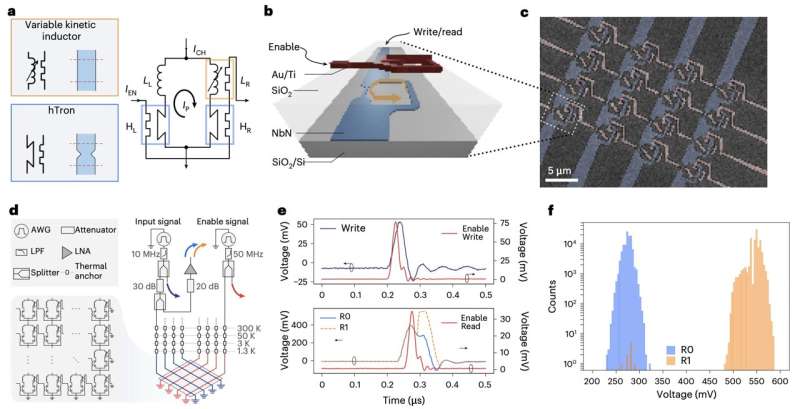

The new memory design focuses on scalable superconducting nanowire technology. The researchers created a compact 4 × 4 memory array consisting of superconducting nanowire loops, featuring two switches and a kinetic inductor. This architecture is designed to operate at a temperature of 1.3 K, enabling stable and predictable performance.

Innovative Design and Functionality

Each memory cell within the array consists of a superconducting nanowire loop that has been engineered to respond dynamically to temperature changes. The kinetic inductor within each cell helps regulate the flow of electrical current, allowing for reliable information storage. The researchers explain, “The arrays operate at 1.3 K, where we implement and characterize multiflux quanta state storage and destructive read-out. By optimizing the write- and read-pulse sequences, we minimize bit errors and maximize operating margins.”

Information is encoded in the memory cells through carefully timed electrical pulses. These pulses temporarily heat one of the nanowire switches, increasing its resistance and allowing a magnetic flux to enter the loop. The magnetic flux represents binary data values (0 or 1). Once the pulse concludes and the nanowire cools, it reverts to its superconducting state, effectively trapping the encoded information.

Initial tests indicate that this new nanowire-based superconducting memory array performs exceptionally well, achieving an impressive bit error rate of approximately 1 in 100,000 operations. This error rate is significantly lower than those observed in previous superconducting memory designs, marking a notable advancement in the field.

Implications for Quantum Computing

The findings from this study could substantially impact the development of superconducting memory systems, bringing them closer to reliable real-world applications. According to the authors, “We achieve a minimum bit error rate of 10−5. We also use circuit-level simulations to understand the memory cell’s dynamics, performance limits, and stability under varying pulse amplitudes.”

The researchers, including Owen Medeiros and Matteo Castellani, emphasize that scalable superconducting memory is crucial for advancing low-energy superconducting computers and fault-tolerant quantum computing systems. As the technology matures, further enhancements and scaling could lead to even more robust memory systems in the future.

This breakthrough represents a significant step forward in the quest for more efficient quantum computing solutions, potentially transforming how data is processed in these next-generation systems. The study reinforces the importance of continued research in superconducting technologies and their applications in the rapidly evolving field of quantum computing.